# ARM-Architecture

# 0. ARM overview

# 0.1 ARM

ARM: Advance RISC Machines.

RISC: Reduced Instruction Set Computer (精简指令集)

- 一个大型统一寄存器文件 (37regs)

- 一个加载 / 存储架构

- 统一固定长度的指令字段 (32bit A64/A32/T32, 16bit T16)

- 简单的寻址模式

- 在每个数据处理指令中对 ALU 和移位器的控制

- 自动递增和自动递减寻址模式

- 有条件地执行所有指令,以最大化执行吞吐量

术语:

- ARMv – (4T, 5TE, 6, 7-A, 8-A) 通用架构名称

- AArch32 - 32 位执行态

- AArch64 - 64 位执行态

- A32, T32 - AArch32 ISA

- A64 - AArch64 ISA

- 32bit 架构和 64 bit 架构之间的交互

- 定义在异常模型里

- AArch64 <=> AArch32

- 指令固定为小端 LE

- 数据可以设置 ELx(0: 小端 1: 大端)

# 0.2 ARM-Serial

Cortex-A

高性能,具备 MMU (VMSA)

可以运行如 Symbian、Linux、Android,Windows CE 等操作系统

智能机等

Cortex-R

- 高端嵌入式满足高性能高可靠性的实时需求

- 基带,存储,车载等

- 可选的 PMSA

Cortex-M

- 嵌入式单片机,低功耗,低成本

- 蓝牙,游戏机等

- 仅支持 thumb 指令

- 可选的 PMSA

# 0.3 ARM-v8-A

Spec:

- 浮点 / NEON 成为指令集一部分

- 8 级以上的流水线,多发射

- 顺序 / 乱序执行

- 直接 / 间接的分支指令预测

- L1(I-cache,D-cache),MMU,L2

- 虚拟化

- 安全拓展插件

# 0.3.1 New-Tech

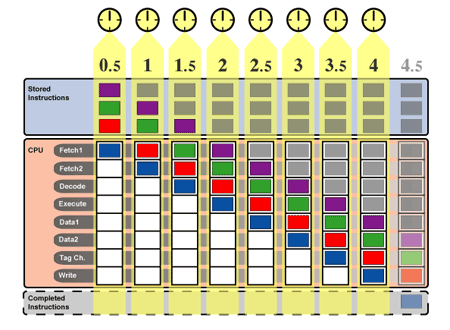

Super Pipeling

加深 pipeline stages 数目的 pipeline 架构,stage 数目通常大于 8

Super scalar

增加 functional units,使的一个时钟周期可以执行多个指令

- 分支指令预测 (Instruction prefetch)

- 取指 (Instruction fetch)

- 解码 (Instruction decode)

- 取寄存器 (Register fetch)

- 发射 (Issue)

- 执行 (Execute)

- 内存访问 (Memory access)

- Load/Store instr

- 寄存器回写 (Register write-back)

- LDR R1, [R4 + 4]!

# 1. ARM Model

# 1.1 AArch32

# 1.1.1 AArch-32 位执行态

A32

32 位固定长度指令集,通过不同架构变体增强部分 32 位架构执行环境。

T32(Thumb - 16bit)

是以 16 位固定长度指令集的形式引入的,随后在引入 Thumb-2 技术时增强为 16 位和 32 位混合长度指令集。

配置如下:

13 x ( 32bit 通用寄存器 和 32bit PC/SP/LR )

不同 PE(处理件)下的 Bank 寄存器

32 x (64bit 寄存器给 SIMD 和 浮点单元使用户)

Single Instruction Multiple Data SMID

32 bit VMSA

A32 和 T32 指令集

- BX #0 操作数寄存器 (0:ARM 1: Thumb)

- BLX 切换在 ARM 和 Thumb 状态

PE 的 PSTATE 状态寄存器

- CPSR

# 1.1.2 AArch-32 Operating Modes

Non-Privileged Mode

- User (usr)

- The normal ARM program execution state

- Unable to change control bits (I,F,T,Mode[0:4]) of Program Status Register

- Unable to access CP15 registers with MRC/MCR instructions

Privileged Mode

FIQ (fiq): Designed to support a data transfer or channel process

RQ (irq): Used for general-purpose interrupt handling

Supervisor (svc): Protected mode for the operating system

Abort mode (abt): Entered after a data or instruction pre-fetch abort

System (sys) : A privileged user mode for the operating system

Undefined (und): Entered When an undefined instruction is executed

| R0(a1) | r0 | r0 | r0 | r0 | r0 |

|---|---|---|---|---|---|

| R1(a2) | R1 | R1 | R1 | R1 | R1 |

| R2(a3) | R2 | R2 | R2 | R2 | R2 |

| R3(a4) | R3 | R3 | R3 | R3 | R3 |

| R4(v1) | R4 | R4 | R4 | R4 | R4 |

| R5(v2) | R5 | R5 | R5 | R5 | R5 |

| R6(v3) | R6 | R6 | R6 | R6 | R6 |

| R7(v4) | R7 | R7 | R7 | R7 | R7 |

| R8(v5) | <u>R8_fiq</u> | R8 | R8 | R8 | R8 |

| R9(v6,SB) | <u>R9_fiq</u> | R9 | R9 | R9 | R9 |

| R10(v7,SL) | <u>R10_fiq</u> | R10 | R10 | R10 | R10 |

| R11(v8,FP) | <u>R11_fiq</u> | R11 | R11 | R11 | R11 |

| R12(IP) | <u>R12_fiq</u> | R12 | R12 | R12 | R12 |

| R13(SP) | <u>R13_fiq</u> | <u>R13_svc</u> | <u>R13_abt</u> | <u>R13_irq</u> | <u>R13_und</u> |

| R14(LR) | <u>R14_fiq</u> | <u>R14_svc</u> | <u>R14_abt</u> | <u>R14_irq</u> | <u>R14_und</u> |

| R15(PC) | R15(PC) | R15(PC) | R15(PC) | R15(PC) | R15(PC) |

| Sys and User | FIQ | SVC | Abort | IFQ | Undefined |

| CPSR | CPSR | CPSR | CPSR | CPSR | CPSR |

| :--: | :-----------------: | :-----------------: | :-----------------: | :-----------------: | :-----------------: |

| <u>SPSR_fiq</u> | <u>SPSR_svc</u> | <u>SPSR_abt</u> | <u>SPSR_irq</u> | <u>SPSR_und</u> |

R13: Used for SP (stack pointer) PUSH and POP

R14:Used for LR (link register)

- 保持 BL/BLX 的下一个指令的地址,一般用于子程序调用

- 在异常状态下返回地址信息

- 也能做一般寄存器使用

R15: Dedicated for PC

指向正在执行的指令之后的两条指令的指针

Two State

ARM: PC = current Addr. instruction + 8 bit[0:1] = 0

Thumb:PC = current Addr. instruction + 4 bit[0] = 0

CPSR:Current program status register

SPSR:Saved program status register used by irq

Sys/User 没有 SPSR

Thumb State <=> ARM State

r0 : R7 -> 访问方式和 ARM 状态下一样 low reg

R8: R12 只能使用 MOV ADD CMP BX 访问

R13:R15 限制访问

CPSR:只能直接访问

SPSR:无法访问

<u>Rx_xxx</u>:属于 bank 寄存器

| 31 | 30 | 29 | 28 | 27 | [26:25] | 24 | [23:20] | [19:16] | [15:10] | 9 | 8 | 7 | 6 | 5 | [4:0] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| N | Z | C | V | Q | IT[1:0] | J | GE[3:0] | E | A | I | F | T | Mode |

[31:24] Flags 🏴

Jazelle state[24] J

加速 Java 程序的执行,已经过时了

Interrupt Type Control[26:25] IT

Saturation for DSP[27] Q

ALU operation overflow[28] V

ALU operation Carry out[29] C

Zero result from ALU[30] Z

Negative result from ALU[31] N

[23:16] Status🕶

- For SIMD instruction[19:16] GE

- Illegal execution state bit[20] IL

- Software Step bit[21] SS

- Reserve[23:22]

[15:8]Extension 🖱

- Imprecise Data Abort disabled [8] A

- Endianness for load/store data [9] E

- interrupt vector[15:10]IT

[7:0]Control 🎛

- Mode [4:0]

| Mode | Operating Mode |

|---|---|

| 0b10000 | User |

| 0b10001 | FIQ |

| 0b10010 | IRQ |

| 0b10011 | Supervisor |

| 0b10111 | Abort |

| 0b11011 | Undefined |

| 0b11111 | System |

- Thumb State[5] T

- FIQ Disable[6] F

- IRQ Disable[7] I

注 1: 软件只能通过 MSR/MSR 指令操作 CPSR/SPSR

注 2: 在用户模式下,只能更改 condition field [31:28]

注 3: 所有 field 都可以在特权模式下更改

注 4: 永远不要强制改变 T 和 J 位,否则处理器将进入不可预知的状态

注 5: filed 可以通过_fsxc 后缀单独访问,例如:MSR SPSR_c, r0

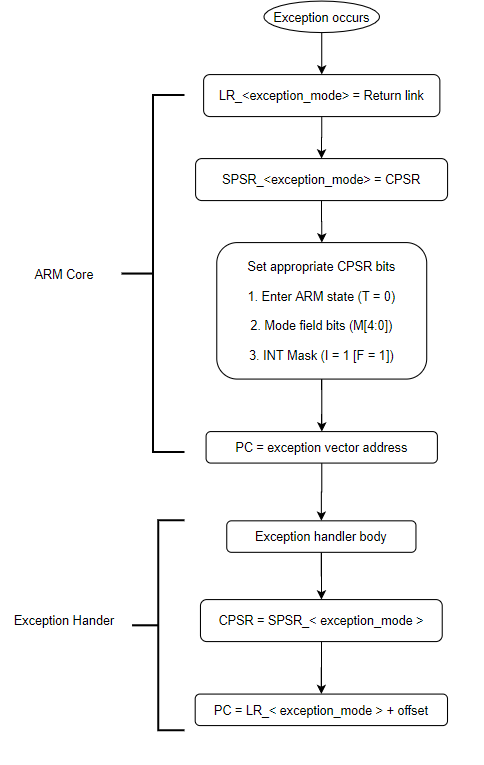

# 1.1.3 AArch-32 Exceptional Procedure

| Exception | Mode | Normal Vector/Hight Vector | Priority | INT Mask | Produce Stage | Return instruction |

|---|---|---|---|---|---|---|

| Reset | Supervisor | 0x00000000/ 0xFFFF0000 | 1 | I, F | nRESET is low | N/A |

| Undefined Instruction | Undefined | 0x00000004/ 0XFFFF0004 | 6 | I | Execute | MOVS PC,R14 |

| SWI | Supervisor | 0x00000008/ 0xFFFF0008 | 6 | I | Execute | MOVS PC,R14 |

| Prefetch Abort | Abort | 0x0000000C/ 0xFFFF000C | 5 | I | Prefetch | SUBS PC ,R14,#4 |

| Data Abort | Abort | 0x00000010/ 0xFFFF0010 | 2 | I | Execute | SUBS PC ,R14,#8 |

| Reserved | N/A | N/A | N/A | N/A | N/A | N/A |

| IRQ | IRQ | 0x00000018/ 0xFFFF0018 | 4 | I | nIRQ is low | SUBS PC ,R14,#4 |

| FIQ | FIQ | 0x0000001C/ 0xFFFF001C | 3 | I, F | nFIQ is low | SUBS PC ,R14,#4 |

注 1: PC 值是异常生成时执行指令的地址

注 2: 无论在哪种状态下生成异常,处理器都将进入 ARM 状态

注 3: 在返回时不需要关心它在进入异常之前的状态。无论 ARM 或 Thumb 的声明,都使用相同的回调地址

Flow

# 1.2 AArch64

# 1.2.1 AArch-64

A64

提供与 ARM 和 Thumb 指令集类似功能的 32 位固定长度指令集。随 ARMv8-A 一起引入,它是一种 AArch64 指令集。

配置如下:

31 x 64bit 通用寄存器 X30 作为 LR

- 64 位寄存器 X0 ~ X30,32 位寄存器 W0 ~ W30

不同 PE(处理件)下的 Bank 寄存器

32 x (128bit 寄存器给 SIMD 和 浮点单元使用)

Single Instruction Multiple Data SMID

64 bit VMSA

A64 指令集

PE 的 PSTATE 状态寄存器

- 不止一个

异常模型:减少 Banked 寄存器 / 模式

- EL0~3 共 4 级异常模型

# 1.2.2 AArch-64 Operating Modes

4 级 EL 代替 8 种不同的处理器模式

类似 x86 架构的 RING

EL0: 非特权等级,应用程序运行在此等级 Usr mode

EL1: 特权等级,用于运行 kernel

EL2: virtualization on Non-secure

- 可运行 Hypervisor

EL3: 支持切换 Secure 态和 Non-secure 态

- 可运行 Secure monitor

EL1~3 有独自的 ELR/SP/SPSR banked 寄存器

实际设计中 EL0 ~ 1 必须,EL2~3 可选。

PE 可能是 EL0,EL1,EL3

64 位 SP (XSP/WSP)

- 必须 16 字节对齐 (否则产生栈对齐异常)

- 在 EL1 可更改这个设定

64 位 PC

- 在不是 4 字节对齐的地址上执行将产生对齐异常

Unbanked 寄存器

- X0 ~ 30,V0 ~ 31

Banked 寄存器

- 主要用于异常返回信息 / SP

| EL0 | EL1 | EL2 | EL3 | ||

|---|---|---|---|---|---|

| SP = Stack Ptr | SP_EL0 | SP_EL1 | SP_EL2 | SP_EL3 | |

| ELR = Exception Link Register | ELR_EL1 | ELR_EL2 | ELR_EL3 | (PC) | |

| Saved/Current Process Status Register | SPSR_EL1 | SPSR_EL2 | SPSR_EL3 | (CPSR) |

| 31 | 30 | 29 | 28 | [27:24] | [23:22] | 21 | 20 | [19:10] | 9 | 8 | 7 | 6 | 5 | 4 | [3:0] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| N | Z | C | V | RES0 | RES0 | SS | IL | RES0 | D | A | I | F | RES0 | M | Mode |

[31:24] Flags 🏴

- Reserve[24:27]

- ALU operation overflow[28] V

- ALU operation Carry out[29] C

- Zero result from ALU[30] Z

- Negative result from ALU[31] N

[23:20] Status🕶

- Illegal execution state bit[20] IL

- Software Step bit[21] SS

- Reserve[23:22]

[19:8]Extension 🖱

- Imprecise Data Abort disabled [8] A

- Debug mask bit [9] D

- RES0[19:10]

[7:0]Control 🎛

- Mode [3:0]

| Mode | Exception level and SP |

|---|---|

| 0b1101 | EL3h |

| 0b1100 | EL3t |

| 0b1001 | EL2h |

| 0b1000 | EL2t |

| 0b0101 | EL1h |

| 0b0100 | EL1t |

| 0b0000 | EL0t |

- Execution State[4] M 1:AArch32 0:AArch64

- Reserve[5]

- FIQ Disable[6] F

- IRQ Disable[7] I

| ILP32 | LP64 | LLP64 | ILP64 | |

|---|---|---|---|---|

| char | 8 | |||

| short | 16 | |||

| int | 32 | 32 | 32 | 64 |

| long | 32 | 64 | 32 | 64 |

| long long | 64 | |||

| size_t | 32 | 64 | 64 | 64 |

| pointer | 32 | 64 | 64 | 64 |

# 1.2.3 AArch-64 Exceptional Procedure

异常返回地址写入 ELR

进入异常时关闭所有中断

异常发生时或返回

- 进入异常:增加 EL 等级或维持不变

- 异常返回:减少 EL 等级或维持不变

EL1~3 有不同的异常向量地址 (VBAR) 寄存器

异常向量包含

异常类型:

synchronous(MMU abort),

IRQ, FIQ or System Error

Exception origin (same or lower EL) and register width

异常原因寄存器 (提供异常细节)

- 异常类型

- 指令长度 (AArch32)

- 指令相关信息

VBAR

# 2. ARM Aarch32 - Aarch64

2 种执行态

AArch64:64 位执行环境

AArch32:32 位执行环境,兼容 ARMv7-A

不同的 EL 等级可以有不同的执行态

EL0 由异常返回信息指定

由高 EL 的系统寄存器指定

| 异常等级 | 组合 1 | 组合 2 | 组合 3 | 组合 4 | 组合 5 |

|---|---|---|---|---|---|

| EL0 | AArch64 | AArch32 | AArch32 | AArch32 | AArch32 |

| EL1 | AArch64 | AArch64 | AArch32 | AArch32 | AArch32 |

| EL2 | AArch64 | AArch64 | AArch64 | AArch32 | AArch32 |

| EL3 | AArch64 | AArch64 | AArch64 | AArch64 | AArch32 |

如图:

当进入高 EL 时有两种策略

- 执行态保持不变

- 由 AArch32 => AArch64

当返回低 EL 时有两种策略

- 执行态保持不变

- 由 AArch64 => AArch32

寄存器映射

| 映射 | X0~X7 | X8~X15 | X15-X23 | X24~X30 |

|---|---|---|---|---|

| 0 | R0 | R8_usr | R14_irq | R8_fiq |

| 1 | R1 | R9_usr | R13_irq | R9_fiq |

| 2 | R2 | R10_usr | R14_svc | R10_fiq |

| 3 | R3 | R11_usr | R13_svc | R11_fiq |

| 4 | R4 | R12_usr | R14_abt | R12_fiq |

| 5 | R5 | R13_usr | R13_abt | R13_fiq |

| 6 | R6 | R14_usr | R14_und | R14_fiq |

| 7 | R7 | R13_hyp | R13_und | N/A |

| AArch32 | AArch64 | |||

| :------: | :------: | |||

| SPSR_svc | SPSR_EL1 | |||

| SPSR_hyp | SPSR_EL2 | |||

| ELR_hyp | ELR_EL2 |

链接只能用各自的库无法混着链接!!!